喜讯!陈文智教授团队论文被顶级期刊TCAD录用

浙江大学计算机系统结构实验室(ARClab)在读博士生林溢泉的论文“PARS: A Pattern-Aware Spatial Data Prefetcher Supporting Multiple Region Sizes”于2024年8月被体系结构领域CCF-A类期刊TCAD录用。该论文由陈文智教授和王总辉老师指导,分析了区域大小对数据预取器的影响;发现现有预取器因单一区域大小设计导致预取性能下降、存储效率低下的问题;并提出了一种可以同时支持多种区域大小的硬件预取器架构PARS,在提升性能的同时降低存储开销。

期刊介绍

TCAD(IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems)是由IEEE出版的一个国际知名学术期刊,是电子设计自动化领域最具影响力的期刊之一,是中国计算机学会(CCF)认定的体系结构领域的A类期刊。

现有预取器仅支持单一区域大小导致的问题

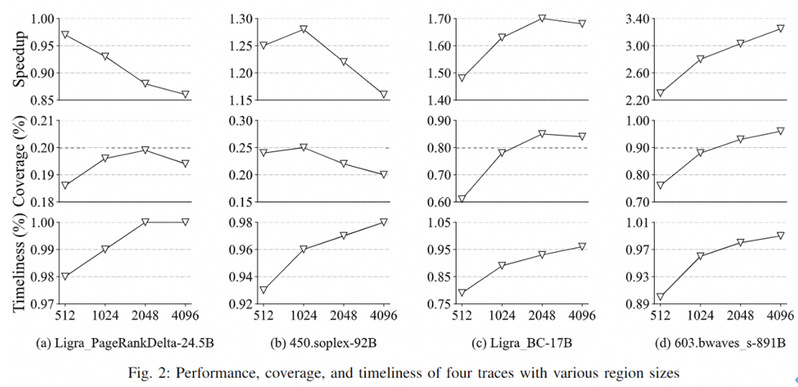

频繁的高速缓存缺失严重限制了应用程序的性能。硬件预取器是一种能有效减少高速缓存缺失次数的技术。它通过预测未来将要访问的数据,提前发出预取请求,将数据加载到高速缓存上,以减少高速缓存缺失,提升程序性能。近年来,空间预取器已经被证实能够有效预测内存访问并提升程序性能。本文对空间预取器进行了详细的分析和研究,发现区域大小这一参数不仅会显著影响预取的性能,还会影响存储的效率。如上图所示,不同的应用程序在获得最佳性能时对应的区域大小不尽相同,这是由于它们的数据结构大小、布局和访问模式的特征存在的差异导致的。因此,不同应用适合采用不同的区域大小设置。然而,现有的空间预取器只能支持单一的区域大小,这样的设计不仅仅限制了预取的优化效果,同时还增加了预取器的存储开销。

模式感知的多区域大小预取架构

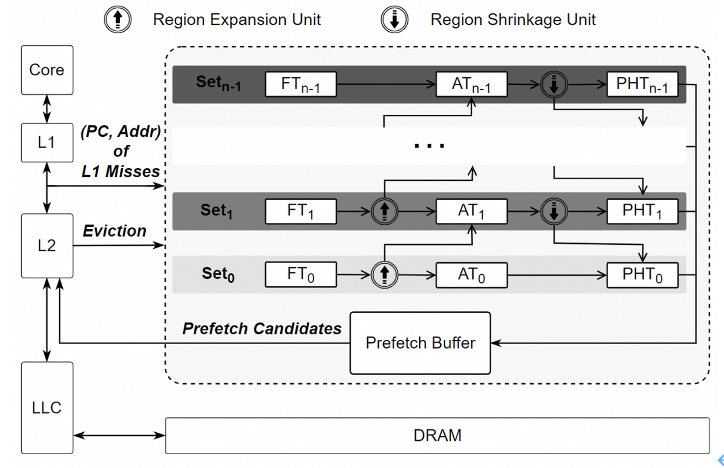

本文提出了PARS,一种可以同时支持多种区域大小的硬件预取器架构。PARS采用多层级的架构,能同时支持对多种区域大小的访问模式的训练和预测。此外,PARS采用了一种自适应调整区域大小的机制,能根据当前的访问模式动态地调整到更合适的区域大小设置,同时实现了预取性能的提升和存储开销的降低。通过对198条公开的应用trace进行仿真模拟,实验结果表明:PARS相比目前最先进的预取器Bingo和Pythia而言,在单核系统下提升了2.1%(最高24.4%)和3.9%(最高111.2%);在四核系统下,提升了5%(最高66.0%)和5.4%(最高177.9%)。在实现性能提升的同时,PARS的存储开销仅为Bingo的17.5%。

作者介绍

论文第一作者林溢泉为浙江大学计算机系统结构实验室(ZJU ARClab)的在读博士生,主要研究方向为微架构性能优化。