FPGA Based Hardware-Software Co-designed Dynamic Binary Translation System

Abstract

Binary translation is used to allow applications of one instruction set architecture (ISA) to run on another, thereby maintaining the binary level compatibility across ISAs. Conventional software binary translation systems suffer performance loss because of architectural heterogeneity amongst ISAs, control flow translation and context switches. In this paper, we propose an FPGA based hardware-software co-designed dynamic binary translation (DBT) system, which moderates these issues at a low level of hardware cost. In our DBT system, we propose a MIPS condition code flags register and a modest ISA extension to bridge the architectural gap, a hardware address mapping mechanism to accelerate the handling of control flow instructions, and a scratchpad memory to reduce performance loss during context switches.

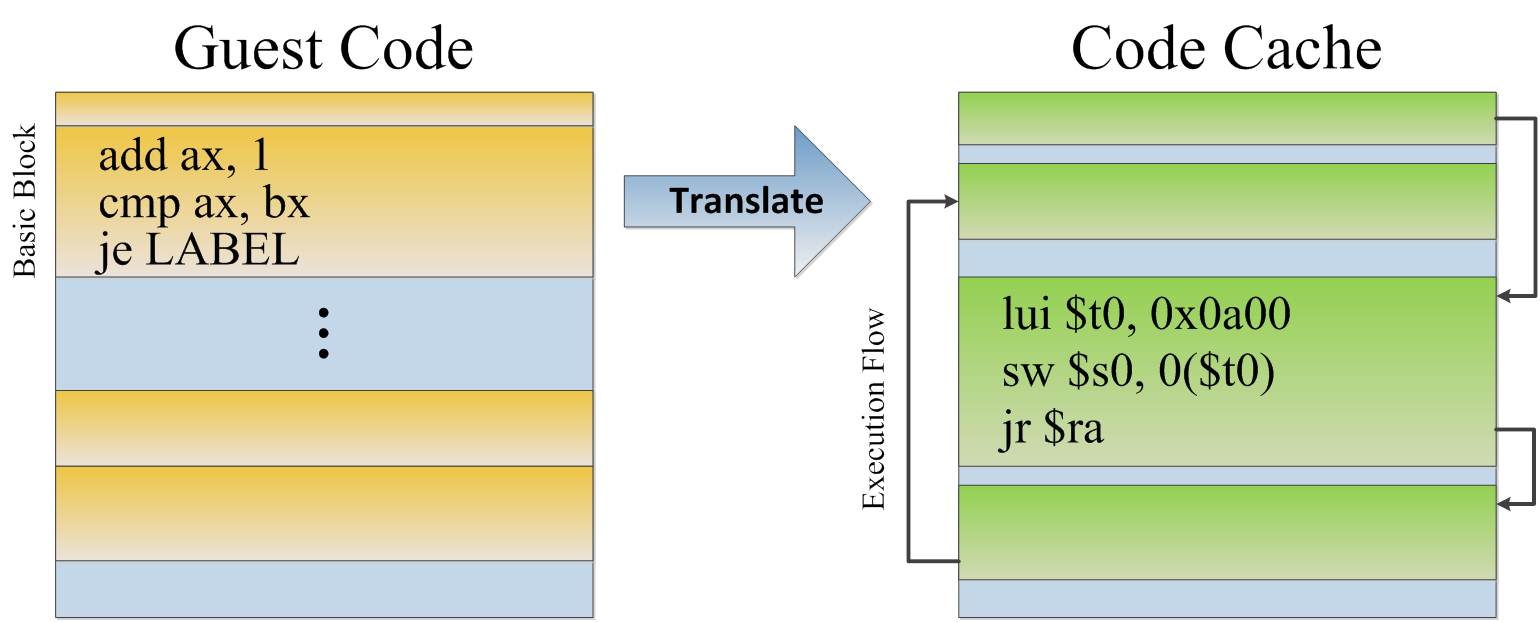

What is Dynamic Binary Translation

Hardware Supports for DBT (x86 -> MIPS)

Heterogeneity among ISAs

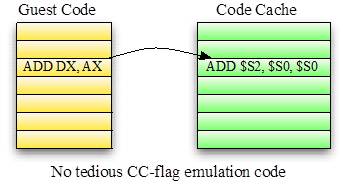

Condition Code Flags (CC-flags)

An x86 compatible CC-flags implemented in MIPS, removes the overhead of CC-flag emulation code

Endianness

Little endian -> big endian

Modest ISA extension for little endian memory access

| Insts | Description |

|---|---|

| LW_LE | Load word in little endian |

| SW_LE | Store word in little endian |

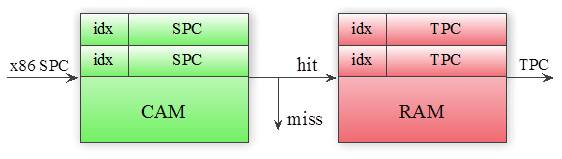

Control flow translation

To translate branch instructions, the jump target PCs are different from the guest code

A hardware Jump-address Lookup Table (JLUT)

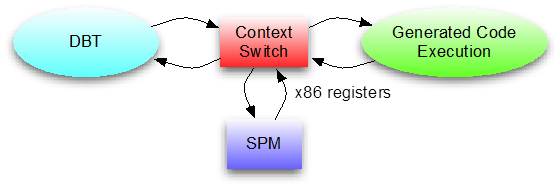

Context Switches

Frequent context switches between the DBT and the generated code execution

An Scratchpad Memory (SPM) to store the switched out emulated registers

Experiment Result

Performance Improvement

Average speedup by 56.1%, using MiBench benchmarks

Resource Utilization

Occupies extra 1.4% of slices and 5.4% of BRAMs of Xilinx Virtex-5 on-chip resources

| Config | Slices | LUTs | F/Fs | BRAMs |

|---|---|---|---|---|

| Baseline | 9.2% | 5.3% | 2.8% | 2.0% |

| SPM | 9.4% | 6.0% | 2.8% | 2.0% |

| JLUT | 10.2% | 6.4% | 3.0% | 7.4% |

| LE | 9.5% | 5.8% | 2.8% | 2.0% |

| ALL | 10.6% | 6.5% | 3.0% | 7.4% |

Copyright Statement

This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder.