# Chapter 6 Multiprocessors and Thread-Level Parallelism

chenwz@zju.edu.cn

2014年4月13日

# 6.1 Introduction

advances in uniprocessor architecture were nearing an end

- processor performance growth was at its highest rate

- parallel processors will definitely have a bigger role in the future

Which is right?

#### 6.2 A Taxonomy of Parallel Architectures

- Single instruction stream, single data stream (SISD) —This category is the uniprocessor.

- Single instruction stream, multiple data streams (SIMD) —Vector architectures are the largest class of processors of this type.

- Multiple instruction streams, single data stream (MISD) —No commercial multiprocessor of this type has been built to date, but may be in the future.

- Multiple instruction streams, multiple data streams (MIMD) —Each processor fetches its own instructions and operates on its own data. The processors are often off-the-shelf microprocessors.

# 6.3 Two classes of MIMD

## Depend On:

- the number of processors

- memory organization

- Interconnect strategy

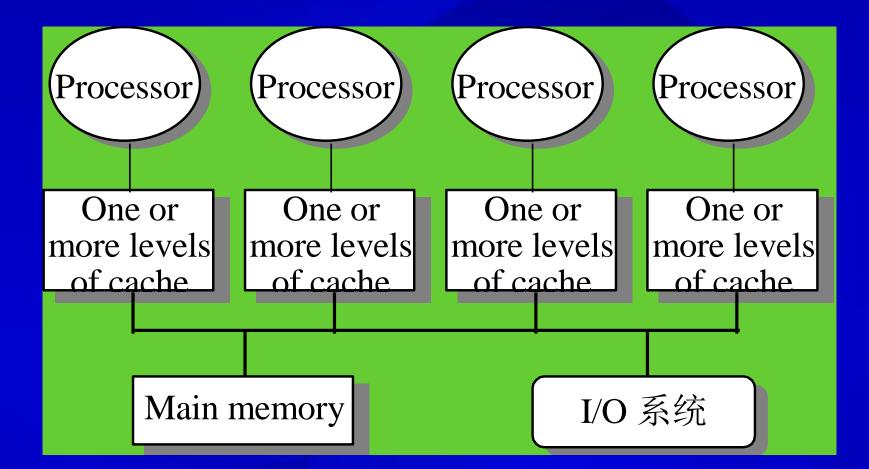

# 6.3.1 centralized shared-memory architecture

- With small processor counts

- With large caches

- Called symmetric (shared-memory) multiprocessors (SMPs)

- Called UMA for uniform memory access

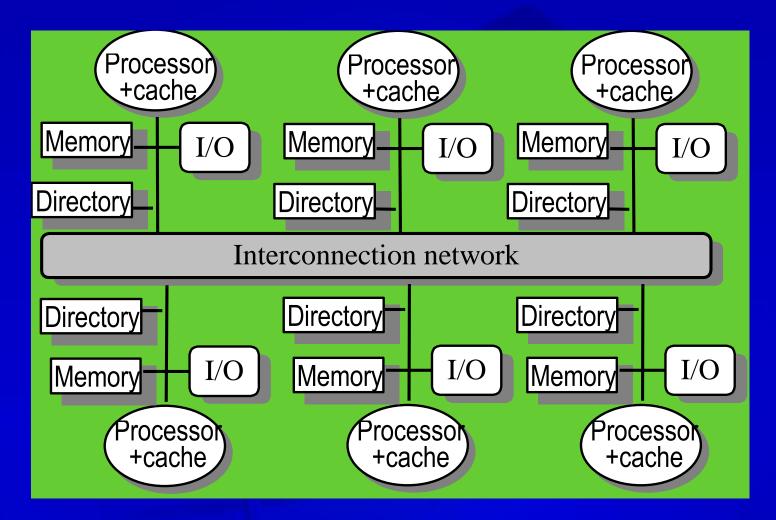

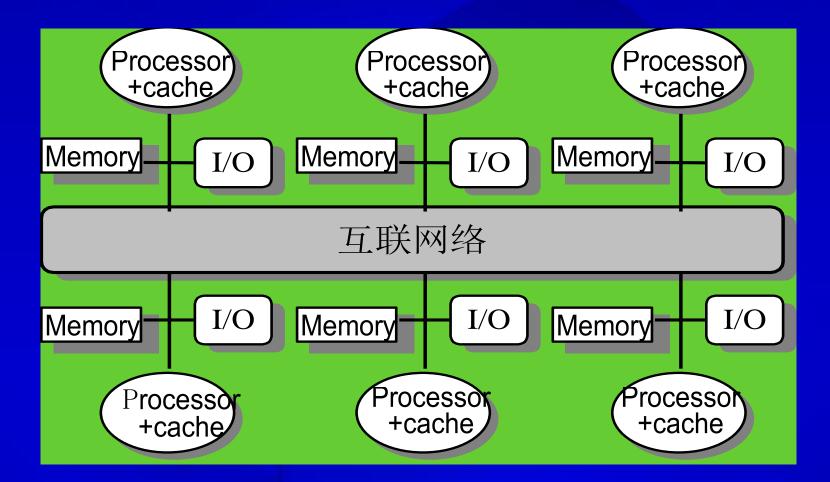

# 6.3.2 distributed-memory architecture

- With large processor counts

- the need for a high bandwidth interconnect

- Advantage:

- cost-effective way to scale the memory bandwidth, if most of accesses are to local memory in the node.

- It reduces the latency for access to the local memory.

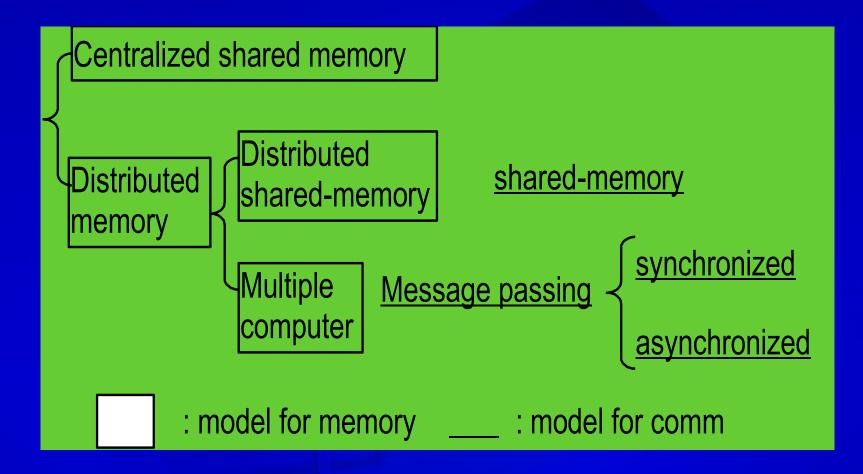

#### 6.4 Models for Communication and Memory Architecture

# 6.4.1 Models for memory Architecture

- Distributed shared memory (DSM or scalable shared memory)

- logical uniform address space but physical distributed memory, so any one of the processors can access any one of the memories.

- Shared memory means sharing the address space, which is different from centralized shared memory.

- UMA( uniform memory access) ---- centralized share memory.

- NUMA( non-uniform memory access) ----distributed shared memory.

#### multiple computers

- Address space consists of multiple private address spaces. cannot be addressed by a remote processor.

- Each processor-memory module is essentially a separate computer (*multicomputers*).

# message nassing

message passing

Synchronous message passing (RPC)

Asynchronous message passing(MPI)

## 6.4.2 Models for Communication

shared memory

#### **For Shared memory**

–compatibility with mechanism used in centralized multiprocessors

- –easy programming, simplify compiler design

- lower overhead for communication and better use of bandwidth, due to implicit nature of communication and implement memory protection in hardware instead of in OS.

- –The ability to use hardware-controlled caching to reduce the frequency of remote communication by supporting automatic caching of both shared and private data.

#### For Message passing

. . . .

- -The hardware can be simpler

- –communication is explicit, simpler to understand

- -forcing programmers and compilers to pay attention to communication.

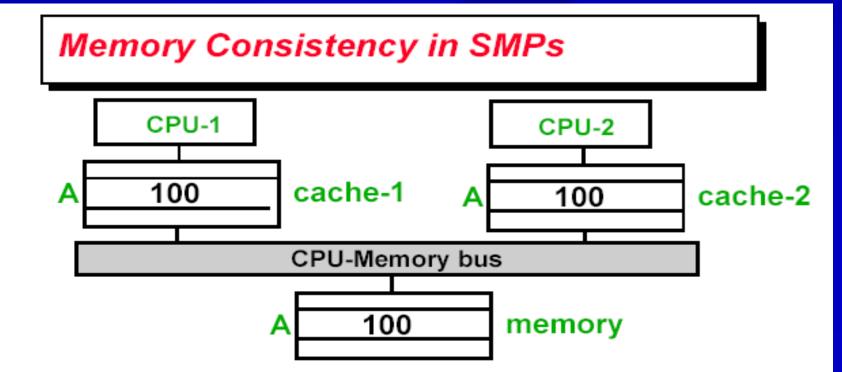

#### 6.5 What Is Multiprocessor Cache Coherence?

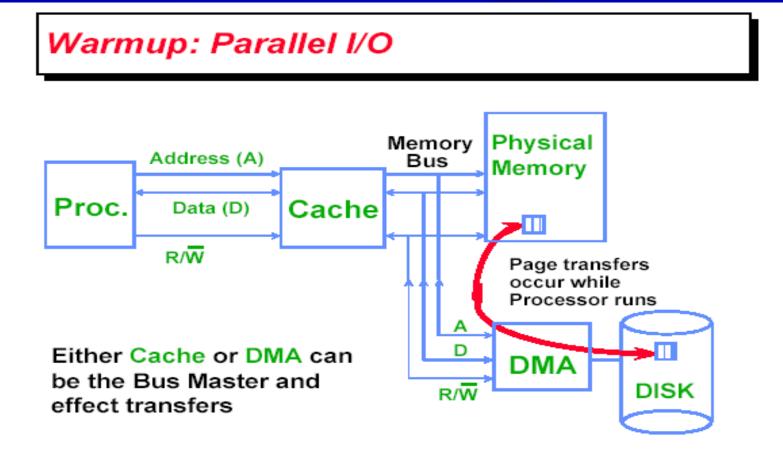

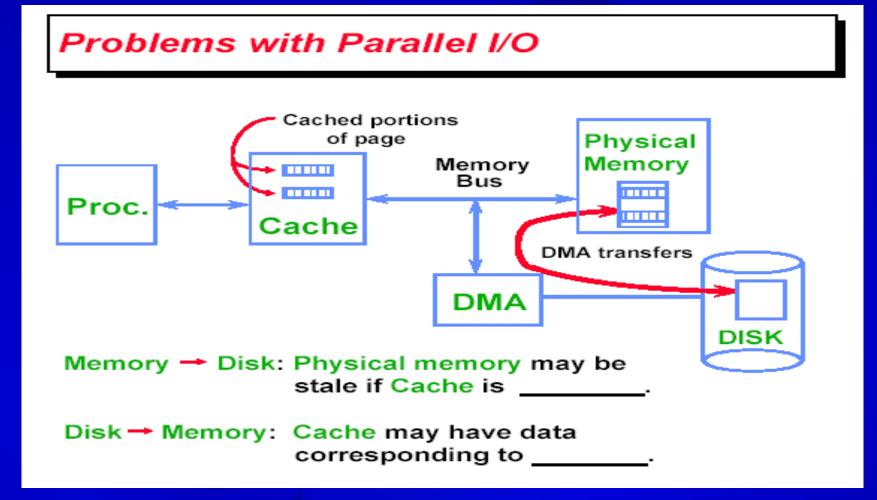

DMA stands for Direct Memory Access

####

Suppose CPU-1 updates A to 200.

write-back: memory and cache-2 have stale values write-through: cache-2 has a stale value

# **Example1: read**

| Time | Event                 | Cache        | Cache        | Memory       |

|------|-----------------------|--------------|--------------|--------------|

|      |                       | contents for | contents for | contents for |

|      |                       | CPU A        | CPU A        | Location X   |

| 0    |                       |              |              | 1            |

| 1    | CPU A reads X         | 1            |              | 1            |

| 2    | CPU B reads X         | 1            | 1            | 1            |

| 3    | CPU A stores 0 into X | 0            | 1            | 0            |

# **Example2: write**

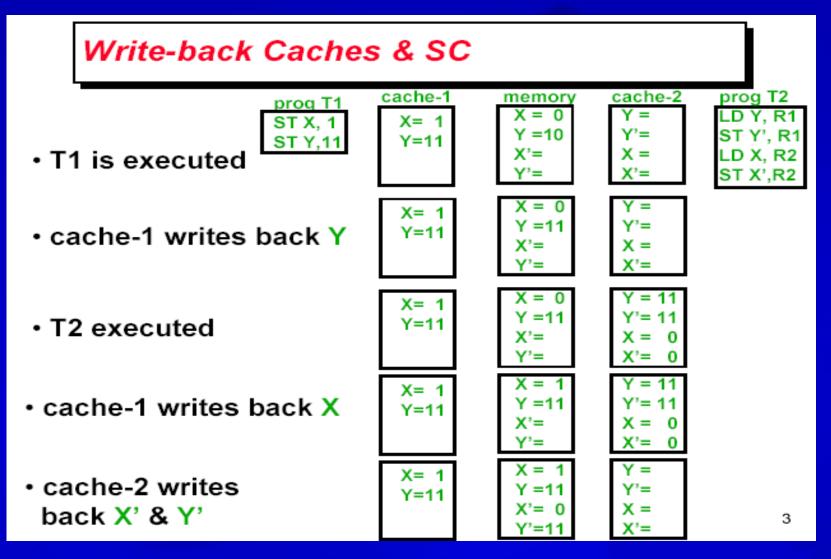

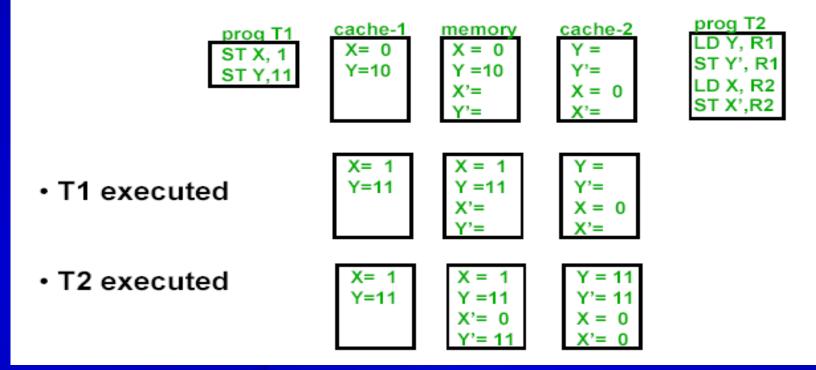

#### Write-through Caches & SC

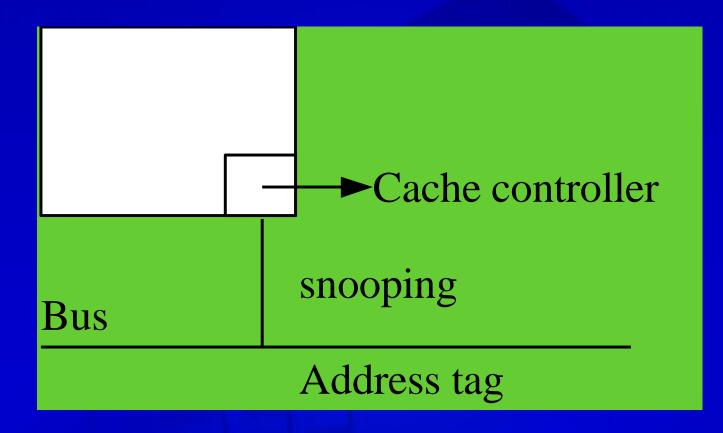

# 6.6 Snooping

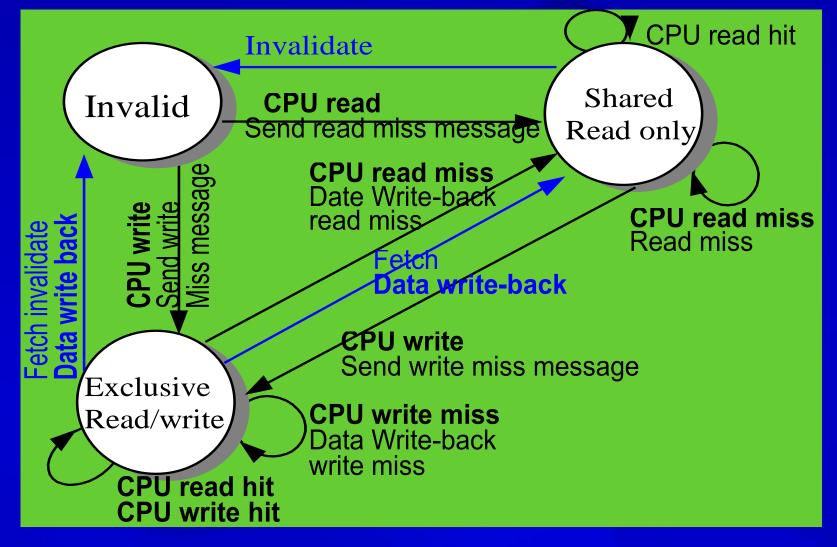

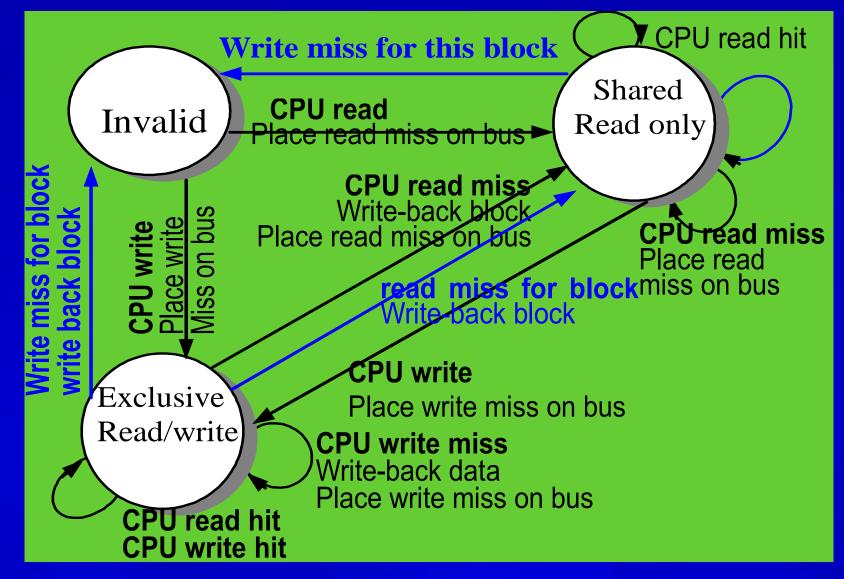

# 6.6.1 Write invalidate protocol

| Processor<br>Activity    | Bus activity          | Contents of<br>CPU A's<br>cache | Contents of<br>CPU B's<br>cache | Contents of<br>Memory<br>Location X |

|--------------------------|-----------------------|---------------------------------|---------------------------------|-------------------------------------|

|                          |                       |                                 |                                 | 0                                   |

| CPU A<br>Reads X         | Cache miss<br>for X   | 0                               |                                 | 0                                   |

| CPU B<br>Reads X         | Cache miss<br>for X   | 0                               | 0                               | 0                                   |

| CPU A writes<br>A 1 to X | Invalidation<br>for X | 1                               |                                 | 0                                   |

| CPU B<br>Reads X         | Cache miss<br>for X   | 1                               | 1                               | 1                                   |

#### **6.6.2Write update or write broadcast protocol**

| Processor<br>Activity    | Bus activity            | Contents of<br>CPU A's<br>cache | Contents of<br>CPU B's<br>cache | Contents of<br>Memory<br>Location X |

|--------------------------|-------------------------|---------------------------------|---------------------------------|-------------------------------------|

|                          |                         |                                 |                                 | 0                                   |

| CPU A<br>Reads X         | Cache miss<br>for X     | 0                               |                                 | 0                                   |

| CPU B<br>Reads X         | Cache miss<br>for X     | 0                               | 0                               | 0                                   |

| CPU A writes<br>A 1 to X | Write broadcast<br>Of X | 1                               |                                 | (j)                                 |

| CPU B<br>Reads X         |                         | 1                               | 1                               | くし                                  |

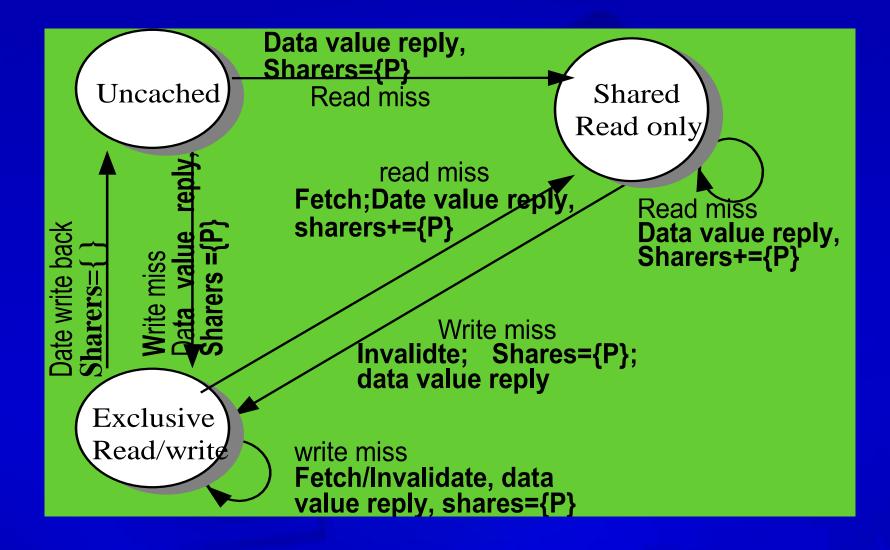

# 6.7 Directory protocol